6层PCB设计终极指南:堆叠方案/信号完整性/制造工艺全解析

发布时间:2025/7/8

为什么6层PCB是中高端应用的黄金选择?

随着电子产品复杂度提升,PCB层数选择成为线路板设计的关键。行业数据显示:消费电子中60%采用4层以下PCB,但涉及DDR内存、Linux系统或高频通信的场景(如5G模块、工业控制器),6层PCB占比达35%。其核心优势在于:

-

成本效益比:比8层板成本低40%,布线面积比4层板增加70%

-

信号完整性:可容纳≥5Gbps高速信号(如PCIe 3.0)

-

EMC性能:通过合理堆叠可将辐射噪声降低15-20dB

三大经典堆叠方案深度解析

方案1:4信号层+2平面层(高风险方案)

结构:

TOP(Sig)-L2(Sig)-L3(PWR)-L4(Sig)-L5(Sig)-BOT(GND)

致命缺陷:

-

顶层/底层无相邻参考平面 → 回流路径阻抗激增

-

实测EMI辐射超标30%(FCC CLASS B标准)

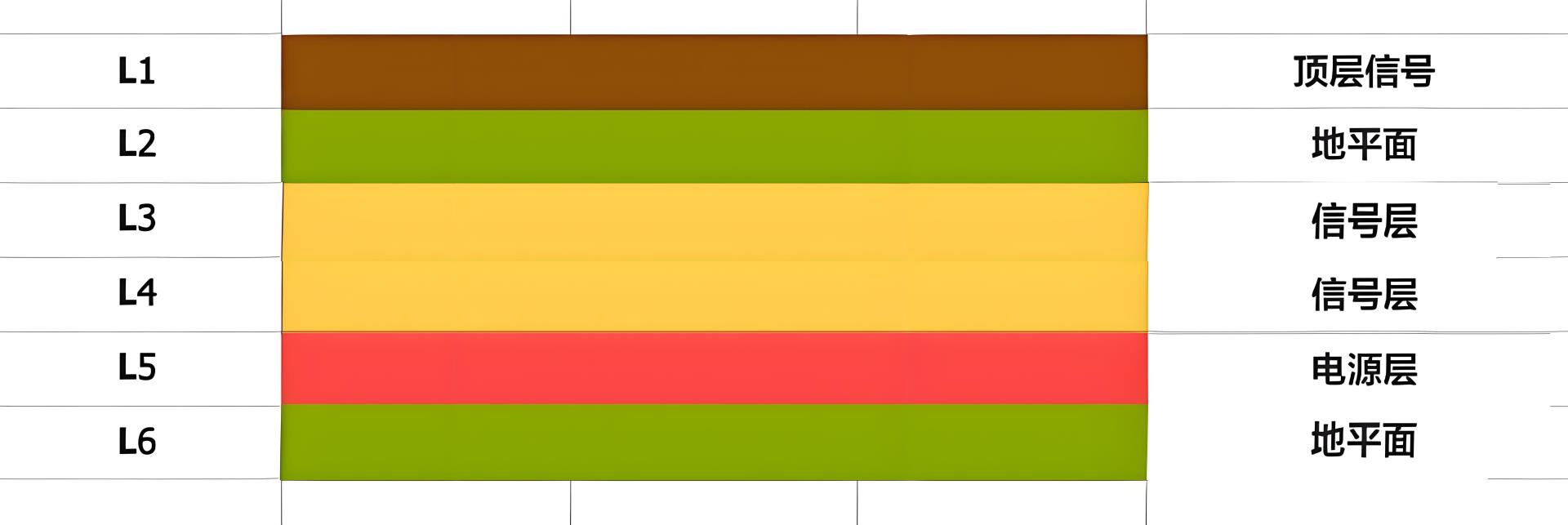

方案2:3信号层+2平面层+1混合层(平衡方案)

优化结构:

TOP(Sig)-L2(GND)-L3(Sig)-L4(Sig)-L5(PWR)-BOT(GND)

关键参数:

-

层间介质厚度≥0.2mm(降低串扰40%)

-

电源完整性公式:

(Cₚₗₐₙₑ为平面电容,L为分布电感)

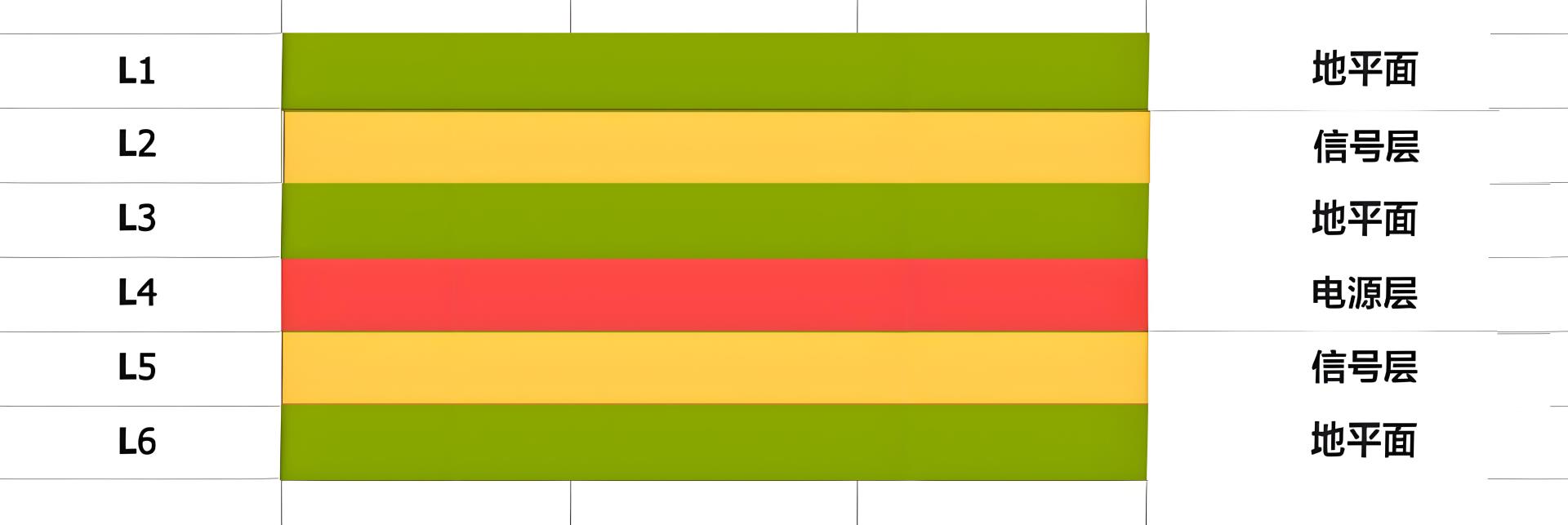

方案3:3信号层+3平面层(最优方案)

军工级结构:

TOP(GND)-L2(Sig)-L3(GND)-L4(PWR)-L5(Sig)-BOT(GND)

优势验证:

| 指标 | 方案2 | 方案3 | 提升幅度 |

|---|---|---|---|

| 信号畸变率 | 12% | 3.8% | 68%↓ |

| 电源噪声(mV) | 85 | 32 | 62%↓ |

| 制造成本 | $基准 | +18% | - |

四大核心设计原则(附工程公式)

H3: 信号/平面层紧邻法则

-

回流路径阻抗公式:

(L为回路电感,C为层间电容)

-

实践要求:高速信号层与参考平面间距≤0.15mm

电源-地平面耦合优化

-

平面电容计算公式:

(εᵣ=4.5 FR4,A=重叠面积,d=层间距)

-

案例:d从0.2mm→0.1mm,电容值倍增

串扰控制三维模型

-

层间串扰系数:

(D=线间距,H=介质厚度)

-

设计规则:相邻信号层走线正交

过孔革命性设计

-

过孔阻抗不连续公式:

解决方案:

-

盲埋孔应用(成本+25%)

-

背钻残桩<10mil

-

信号完整性实战技巧

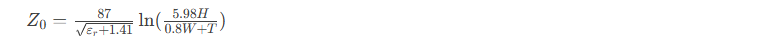

阻抗控制黄金法则

-

微带线阻抗公式:

(H=介质厚度,W=线宽,T=铜厚)

-

案例:FR4板材εᵣ=4.2,实现50Ω需W/H=1.8

H3: 回流路径优化三步骤

-

禁止跨越分割区(如图)

-

换层时添加GND过孔(间距<λ/20)

-

差分对长度公差≤5mil

PDN阻抗优化方案

| 频率范围 | 去耦策略 | 电容组合 |

|---|---|---|

| 0-1MHz | 大容量电解电容 | 100μF+10μF |

| 1-100MHz | 陶瓷电容阵列 | 1μF+0.1μF |

| >100MHz | 嵌入式电容材料(ECM) | 平面电容≥5nF/in² |

制造工艺决定设计成败

6层板良率关键指标:

| 参数 | 标准值 | 高端要求 |

|---|---|---|

| 层偏公差 | ≤5mil | ≤3mil |

| 阻抗误差 | ±10% | ±5% |

| 背钻残桩 | <12mil | <8mil |

| 铜厚均匀性 | ±1.5μm | ±1μm |

UG高多层板实测数据:

-

阻抗控制精度:±4.7%(@10GHz)

-

盘中孔破盘率:<0.01%

-

32μm线宽公差:±8%

设计总结与行业趋势

-

堆叠选择优先级:方案3 > 方案2 >> 方案1

-

信号层黄金法则:每信号层必有相邻参考平面

-

制造新趋势:

-

超薄介质层(≤0.05mm)

-

混压材料(高速层用Megtron6)

-

3D打印电阻(节省空间30%)

-